Loading...

Searching...

No Matches

cdce906_reg.h File Reference

CDCE906 PLL register definitions. More...

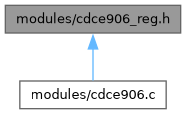

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Enumerations | |

| enum | cdce906_clkin_src { CDCE906_CLKIN_SRC_CRYSTAL = 0b00 , CDCE906_CLKIN_SRC_LVCMOS = 0b01 , CDCE906_CLKIN_SRC_DIFF = 0b10 } |

Detailed Description

CDCE906 PLL register definitions.

Macro Definition Documentation

◆ CDCE906_CLKIN_SRC_BYTE

| #define CDCE906_CLKIN_SRC_BYTE 11 |

◆ CDCE906_CLKIN_SRC_MASK

| #define CDCE906_CLKIN_SRC_MASK 0xC0 |

◆ CDCE906_CLKIN_SRC_SHIFT

| #define CDCE906_CLKIN_SRC_SHIFT 6 |

◆ CDCE906_CLKSEL_BYTE

| #define CDCE906_CLKSEL_BYTE 10 |

◆ CDCE906_CLKSEL_MASK

| #define CDCE906_CLKSEL_MASK 0x10 |

◆ CDCE906_CLKSEL_SHIFT

| #define CDCE906_CLKSEL_SHIFT 4 |

◆ CDCE906_EECNT_BYTE

| #define CDCE906_EECNT_BYTE 26 |

◆ CDCE906_EECNT_MASK

| #define CDCE906_EECNT_MASK 0x7F |

◆ CDCE906_EECNT_SHIFT

| #define CDCE906_EECNT_SHIFT 0 |

◆ CDCE906_EELOCK_BYTE

| #define CDCE906_EELOCK_BYTE 25 |

◆ CDCE906_EELOCK_MASK

| #define CDCE906_EELOCK_MASK 0x80 |

◆ CDCE906_EELOCK_SHIFT

| #define CDCE906_EELOCK_SHIFT 7 |

◆ CDCE906_EEPIP_BYTE

| #define CDCE906_EEPIP_BYTE 24 |

◆ CDCE906_EEPIP_MASK

| #define CDCE906_EEPIP_MASK 0x80 |

◆ CDCE906_EEPIP_SHIFT

| #define CDCE906_EEPIP_SHIFT 7 |

◆ CDCE906_EEWRITE_BYTE

| #define CDCE906_EEWRITE_BYTE 26 |

◆ CDCE906_EEWRITE_MASK

| #define CDCE906_EEWRITE_MASK 0x80 |

◆ CDCE906_EEWRITE_SHIFT

| #define CDCE906_EEWRITE_SHIFT 7 |

◆ CDCE906_P0_DIV_BYTE

| #define CDCE906_P0_DIV_BYTE 13 |

◆ CDCE906_P0_DIV_MASK

| #define CDCE906_P0_DIV_MASK 0x7F |

◆ CDCE906_P0_DIV_SHIFT

| #define CDCE906_P0_DIV_SHIFT 0 |

◆ CDCE906_P0_SW_A_BYTE

| #define CDCE906_P0_SW_A_BYTE 9 |

◆ CDCE906_P0_SW_A_MASK

| #define CDCE906_P0_SW_A_MASK 0xE0 |

◆ CDCE906_P0_SW_A_SHIFT

| #define CDCE906_P0_SW_A_SHIFT 5 |

◆ CDCE906_P1_DIV_BYTE

| #define CDCE906_P1_DIV_BYTE 14 |

◆ CDCE906_P1_DIV_MASK

| #define CDCE906_P1_DIV_MASK 0x7F |

◆ CDCE906_P1_DIV_SHIFT

| #define CDCE906_P1_DIV_SHIFT 0 |

◆ CDCE906_P1_SW_A_BYTE

| #define CDCE906_P1_SW_A_BYTE 10 |

◆ CDCE906_P1_SW_A_MASK

| #define CDCE906_P1_SW_A_MASK 0xE0 |

◆ CDCE906_P1_SW_A_SHIFT

| #define CDCE906_P1_SW_A_SHIFT 5 |

◆ CDCE906_P2_DIV_BYTE

| #define CDCE906_P2_DIV_BYTE 15 |

◆ CDCE906_P2_DIV_MASK

| #define CDCE906_P2_DIV_MASK 0x7F |

◆ CDCE906_P2_DIV_SHIFT

| #define CDCE906_P2_DIV_SHIFT 0 |

◆ CDCE906_P2_SW_A_BYTE

| #define CDCE906_P2_SW_A_BYTE 11 |

◆ CDCE906_P2_SW_A_MASK

| #define CDCE906_P2_SW_A_MASK 0x07 |

◆ CDCE906_P2_SW_A_SHIFT

| #define CDCE906_P2_SW_A_SHIFT 0 |

◆ CDCE906_P3_DIV_BYTE

| #define CDCE906_P3_DIV_BYTE 16 |

◆ CDCE906_P3_DIV_MASK

| #define CDCE906_P3_DIV_MASK 0x7F |

◆ CDCE906_P3_DIV_SHIFT

| #define CDCE906_P3_DIV_SHIFT 0 |

◆ CDCE906_P3_SW_A_BYTE

| #define CDCE906_P3_SW_A_BYTE 11 |

◆ CDCE906_P3_SW_A_MASK

| #define CDCE906_P3_SW_A_MASK 0x38 |

◆ CDCE906_P3_SW_A_SHIFT

| #define CDCE906_P3_SW_A_SHIFT 3 |

◆ CDCE906_P4_DIV_BYTE

| #define CDCE906_P4_DIV_BYTE 17 |

◆ CDCE906_P4_DIV_MASK

| #define CDCE906_P4_DIV_MASK 0x7F |

◆ CDCE906_P4_DIV_SHIFT

| #define CDCE906_P4_DIV_SHIFT 0 |

◆ CDCE906_P4_SW_A_BYTE

| #define CDCE906_P4_SW_A_BYTE 12 |

◆ CDCE906_P4_SW_A_MASK

| #define CDCE906_P4_SW_A_MASK 0x07 |

◆ CDCE906_P4_SW_A_SHIFT

| #define CDCE906_P4_SW_A_SHIFT 0 |

◆ CDCE906_P5_DIV_BYTE

| #define CDCE906_P5_DIV_BYTE 18 |

◆ CDCE906_P5_DIV_MASK

| #define CDCE906_P5_DIV_MASK 0x7F |

◆ CDCE906_P5_DIV_SHIFT

| #define CDCE906_P5_DIV_SHIFT 0 |

◆ CDCE906_P5_SW_A_BYTE

| #define CDCE906_P5_SW_A_BYTE 12 |

◆ CDCE906_P5_SW_A_MASK

| #define CDCE906_P5_SW_A_MASK 0x38 |

◆ CDCE906_P5_SW_A_SHIFT

| #define CDCE906_P5_SW_A_SHIFT 3 |

◆ CDCE906_PLL1_FVCO_BYTE

| #define CDCE906_PLL1_FVCO_BYTE 6 |

◆ CDCE906_PLL1_FVCO_MASK

| #define CDCE906_PLL1_FVCO_MASK 0x80 |

◆ CDCE906_PLL1_FVCO_SHIFT

| #define CDCE906_PLL1_FVCO_SHIFT 7 |

◆ CDCE906_PLL1_REF_DIV_M_HIGH_BYTE

| #define CDCE906_PLL1_REF_DIV_M_HIGH_BYTE 3 |

◆ CDCE906_PLL1_REF_DIV_M_HIGH_MASK

| #define CDCE906_PLL1_REF_DIV_M_HIGH_MASK 0x01 |

◆ CDCE906_PLL1_REF_DIV_M_HIGH_SHIFT

| #define CDCE906_PLL1_REF_DIV_M_HIGH_SHIFT 0 |

◆ CDCE906_PLL1_REF_DIV_M_LOW_BYTE

| #define CDCE906_PLL1_REF_DIV_M_LOW_BYTE 1 |

◆ CDCE906_PLL1_REF_DIV_M_LOW_MASK

| #define CDCE906_PLL1_REF_DIV_M_LOW_MASK 0xFF |

◆ CDCE906_PLL1_REF_DIV_M_LOW_SHIFT

| #define CDCE906_PLL1_REF_DIV_M_LOW_SHIFT 0 |

◆ CDCE906_PLL1_REF_DIV_N_HIGH_BYTE

| #define CDCE906_PLL1_REF_DIV_N_HIGH_BYTE 3 |

◆ CDCE906_PLL1_REF_DIV_N_HIGH_MASK

| #define CDCE906_PLL1_REF_DIV_N_HIGH_MASK 0x1E |

◆ CDCE906_PLL1_REF_DIV_N_HIGH_SHIFT

| #define CDCE906_PLL1_REF_DIV_N_HIGH_SHIFT 1 |

◆ CDCE906_PLL1_REF_DIV_N_LOW_BYTE

| #define CDCE906_PLL1_REF_DIV_N_LOW_BYTE 2 |

◆ CDCE906_PLL1_REF_DIV_N_LOW_MASK

| #define CDCE906_PLL1_REF_DIV_N_LOW_MASK 0xFF |

◆ CDCE906_PLL1_REF_DIV_N_LOW_SHIFT

| #define CDCE906_PLL1_REF_DIV_N_LOW_SHIFT 0 |

◆ CDCE906_PLL1_VCO_MUX_BYTE

| #define CDCE906_PLL1_VCO_MUX_BYTE 3 |

◆ CDCE906_PLL1_VCO_MUX_MASK

| #define CDCE906_PLL1_VCO_MUX_MASK 0x80 |

◆ CDCE906_PLL1_VCO_MUX_SHIFT

| #define CDCE906_PLL1_VCO_MUX_SHIFT 7 |

◆ CDCE906_PLL2_FVCO_BYTE

| #define CDCE906_PLL2_FVCO_BYTE 6 |

◆ CDCE906_PLL2_FVCO_MASK

| #define CDCE906_PLL2_FVCO_MASK 0x40 |

◆ CDCE906_PLL2_FVCO_SHIFT

| #define CDCE906_PLL2_FVCO_SHIFT 6 |

◆ CDCE906_PLL2_REF_DIV_M_HIGH_BYTE

| #define CDCE906_PLL2_REF_DIV_M_HIGH_BYTE 6 |

◆ CDCE906_PLL2_REF_DIV_M_HIGH_MASK

| #define CDCE906_PLL2_REF_DIV_M_HIGH_MASK 0x01 |

◆ CDCE906_PLL2_REF_DIV_M_HIGH_SHIFT

| #define CDCE906_PLL2_REF_DIV_M_HIGH_SHIFT 0 |

◆ CDCE906_PLL2_REF_DIV_M_LOW_BYTE

| #define CDCE906_PLL2_REF_DIV_M_LOW_BYTE 4 |

◆ CDCE906_PLL2_REF_DIV_M_LOW_MASK

| #define CDCE906_PLL2_REF_DIV_M_LOW_MASK 0xFF |

◆ CDCE906_PLL2_REF_DIV_M_LOW_SHIFT

| #define CDCE906_PLL2_REF_DIV_M_LOW_SHIFT 0 |

◆ CDCE906_PLL2_REF_DIV_N_HIGH_BYTE

| #define CDCE906_PLL2_REF_DIV_N_HIGH_BYTE 6 |

◆ CDCE906_PLL2_REF_DIV_N_HIGH_MASK

| #define CDCE906_PLL2_REF_DIV_N_HIGH_MASK 0x1E |

◆ CDCE906_PLL2_REF_DIV_N_HIGH_SHIFT

| #define CDCE906_PLL2_REF_DIV_N_HIGH_SHIFT 1 |

◆ CDCE906_PLL2_REF_DIV_N_LOW_BYTE

| #define CDCE906_PLL2_REF_DIV_N_LOW_BYTE 5 |

◆ CDCE906_PLL2_REF_DIV_N_LOW_MASK

| #define CDCE906_PLL2_REF_DIV_N_LOW_MASK 0xFF |

◆ CDCE906_PLL2_REF_DIV_N_LOW_SHIFT

| #define CDCE906_PLL2_REF_DIV_N_LOW_SHIFT 0 |

◆ CDCE906_PLL2_VCO_MUX_BYTE

| #define CDCE906_PLL2_VCO_MUX_BYTE 3 |

◆ CDCE906_PLL2_VCO_MUX_MASK

| #define CDCE906_PLL2_VCO_MUX_MASK 0x40 |

◆ CDCE906_PLL2_VCO_MUX_SHIFT

| #define CDCE906_PLL2_VCO_MUX_SHIFT 6 |

◆ CDCE906_PLL3_FVCO_BYTE

| #define CDCE906_PLL3_FVCO_BYTE 6 |

◆ CDCE906_PLL3_FVCO_MASK

| #define CDCE906_PLL3_FVCO_MASK 0x20 |

◆ CDCE906_PLL3_FVCO_SHIFT

| #define CDCE906_PLL3_FVCO_SHIFT 5 |

◆ CDCE906_PLL3_REF_DIV_M_HIGH_BYTE

| #define CDCE906_PLL3_REF_DIV_M_HIGH_BYTE 9 |

◆ CDCE906_PLL3_REF_DIV_M_HIGH_MASK

| #define CDCE906_PLL3_REF_DIV_M_HIGH_MASK 0x01 |

◆ CDCE906_PLL3_REF_DIV_M_HIGH_SHIFT

| #define CDCE906_PLL3_REF_DIV_M_HIGH_SHIFT 0 |

◆ CDCE906_PLL3_REF_DIV_M_LOW_BYTE

| #define CDCE906_PLL3_REF_DIV_M_LOW_BYTE 7 |

◆ CDCE906_PLL3_REF_DIV_M_LOW_MASK

| #define CDCE906_PLL3_REF_DIV_M_LOW_MASK 0xFF |

◆ CDCE906_PLL3_REF_DIV_M_LOW_SHIFT

| #define CDCE906_PLL3_REF_DIV_M_LOW_SHIFT 0 |

◆ CDCE906_PLL3_REF_DIV_N_HIGH_BYTE

| #define CDCE906_PLL3_REF_DIV_N_HIGH_BYTE 9 |

◆ CDCE906_PLL3_REF_DIV_N_HIGH_MASK

| #define CDCE906_PLL3_REF_DIV_N_HIGH_MASK 0x1E |

◆ CDCE906_PLL3_REF_DIV_N_HIGH_SHIFT

| #define CDCE906_PLL3_REF_DIV_N_HIGH_SHIFT 1 |

◆ CDCE906_PLL3_REF_DIV_N_LOW_BYTE

| #define CDCE906_PLL3_REF_DIV_N_LOW_BYTE 8 |

◆ CDCE906_PLL3_REF_DIV_N_LOW_MASK

| #define CDCE906_PLL3_REF_DIV_N_LOW_MASK 0xFF |

◆ CDCE906_PLL3_REF_DIV_N_LOW_SHIFT

| #define CDCE906_PLL3_REF_DIV_N_LOW_SHIFT 0 |

◆ CDCE906_PLL3_VCO_MUX_BYTE

| #define CDCE906_PLL3_VCO_MUX_BYTE 3 |

◆ CDCE906_PLL3_VCO_MUX_MASK

| #define CDCE906_PLL3_VCO_MUX_MASK 0x20 |

◆ CDCE906_PLL3_VCO_MUX_SHIFT

| #define CDCE906_PLL3_VCO_MUX_SHIFT 5 |

◆ CDCE906_POWER_DOWN_BYTE

| #define CDCE906_POWER_DOWN_BYTE 12 |

◆ CDCE906_POWER_DOWN_MASK

| #define CDCE906_POWER_DOWN_MASK 0x40 |

◆ CDCE906_POWER_DOWN_SHIFT

| #define CDCE906_POWER_DOWN_SHIFT 6 |

◆ CDCE906_S0_IN_CFG_BYTE

| #define CDCE906_S0_IN_CFG_BYTE 10 |

◆ CDCE906_S0_IN_CFG_MASK

| #define CDCE906_S0_IN_CFG_MASK 0x03 |

◆ CDCE906_S0_IN_CFG_SHIFT

| #define CDCE906_S0_IN_CFG_SHIFT 0 |

◆ CDCE906_S1_IN_CFG_BYTE

| #define CDCE906_S1_IN_CFG_BYTE 10 |

◆ CDCE906_S1_IN_CFG_MASK

| #define CDCE906_S1_IN_CFG_MASK 0x0C |

◆ CDCE906_S1_IN_CFG_SHIFT

| #define CDCE906_S1_IN_CFG_SHIFT 2 |

◆ CDCE906_SSC_FREQ_SEL_BYTE

| #define CDCE906_SSC_FREQ_SEL_BYTE 25 |

◆ CDCE906_SSC_FREQ_SEL_MASK

| #define CDCE906_SSC_FREQ_SEL_MASK 0x0F |

◆ CDCE906_SSC_FREQ_SEL_SHIFT

| #define CDCE906_SSC_FREQ_SEL_SHIFT 0 |

◆ CDCE906_SSC_MOD_SEL_BYTE

| #define CDCE906_SSC_MOD_SEL_BYTE 25 |

◆ CDCE906_SSC_MOD_SEL_MASK

| #define CDCE906_SSC_MOD_SEL_MASK 0x70 |

◆ CDCE906_SSC_MOD_SEL_SHIFT

| #define CDCE906_SSC_MOD_SEL_SHIFT 4 |

◆ CDCE906_Y0_EN_BYTE

| #define CDCE906_Y0_EN_BYTE 19 |

◆ CDCE906_Y0_EN_MASK

| #define CDCE906_Y0_EN_MASK 0x08 |

◆ CDCE906_Y0_EN_SHIFT

| #define CDCE906_Y0_EN_SHIFT 3 |

◆ CDCE906_Y0_POL_BYTE

| #define CDCE906_Y0_POL_BYTE 19 |

◆ CDCE906_Y0_POL_MASK

| #define CDCE906_Y0_POL_MASK 0x40 |

◆ CDCE906_Y0_POL_SHIFT

| #define CDCE906_Y0_POL_SHIFT 6 |

◆ CDCE906_Y0_SLEW_RATE_BYTE

| #define CDCE906_Y0_SLEW_RATE_BYTE 19 |

◆ CDCE906_Y0_SLEW_RATE_MASK

| #define CDCE906_Y0_SLEW_RATE_MASK 0x30 |

◆ CDCE906_Y0_SLEW_RATE_SHIFT

| #define CDCE906_Y0_SLEW_RATE_SHIFT 4 |

◆ CDCE906_Y0_SW_B_BYTE

| #define CDCE906_Y0_SW_B_BYTE 19 |

◆ CDCE906_Y0_SW_B_MASK

| #define CDCE906_Y0_SW_B_MASK 0x07 |

◆ CDCE906_Y0_SW_B_SHIFT

| #define CDCE906_Y0_SW_B_SHIFT 0 |

◆ CDCE906_Y1_EN_BYTE

| #define CDCE906_Y1_EN_BYTE 20 |

◆ CDCE906_Y1_EN_MASK

| #define CDCE906_Y1_EN_MASK 0x08 |

◆ CDCE906_Y1_EN_SHIFT

| #define CDCE906_Y1_EN_SHIFT 3 |

◆ CDCE906_Y1_POL_BYTE

| #define CDCE906_Y1_POL_BYTE 20 |

◆ CDCE906_Y1_POL_MASK

| #define CDCE906_Y1_POL_MASK 0x40 |

◆ CDCE906_Y1_POL_SHIFT

| #define CDCE906_Y1_POL_SHIFT 6 |

◆ CDCE906_Y1_SLEW_RATE_BYTE

| #define CDCE906_Y1_SLEW_RATE_BYTE 20 |

◆ CDCE906_Y1_SLEW_RATE_MASK

| #define CDCE906_Y1_SLEW_RATE_MASK 0x30 |

◆ CDCE906_Y1_SLEW_RATE_SHIFT

| #define CDCE906_Y1_SLEW_RATE_SHIFT 4 |

◆ CDCE906_Y1_SW_B_BYTE

| #define CDCE906_Y1_SW_B_BYTE 20 |

◆ CDCE906_Y1_SW_B_MASK

| #define CDCE906_Y1_SW_B_MASK 0x07 |

◆ CDCE906_Y1_SW_B_SHIFT

| #define CDCE906_Y1_SW_B_SHIFT 0 |

◆ CDCE906_Y2_EN_BYTE

| #define CDCE906_Y2_EN_BYTE 21 |

◆ CDCE906_Y2_EN_MASK

| #define CDCE906_Y2_EN_MASK 0x08 |

◆ CDCE906_Y2_EN_SHIFT

| #define CDCE906_Y2_EN_SHIFT 3 |

◆ CDCE906_Y2_POL_BYTE

| #define CDCE906_Y2_POL_BYTE 21 |

◆ CDCE906_Y2_POL_MASK

| #define CDCE906_Y2_POL_MASK 0x40 |

◆ CDCE906_Y2_POL_SHIFT

| #define CDCE906_Y2_POL_SHIFT 6 |

◆ CDCE906_Y2_SLEW_RATE_BYTE

| #define CDCE906_Y2_SLEW_RATE_BYTE 21 |

◆ CDCE906_Y2_SLEW_RATE_MASK

| #define CDCE906_Y2_SLEW_RATE_MASK 0x30 |

◆ CDCE906_Y2_SLEW_RATE_SHIFT

| #define CDCE906_Y2_SLEW_RATE_SHIFT 4 |

◆ CDCE906_Y2_SW_B_BYTE

| #define CDCE906_Y2_SW_B_BYTE 21 |

◆ CDCE906_Y2_SW_B_MASK

| #define CDCE906_Y2_SW_B_MASK 0x07 |

◆ CDCE906_Y2_SW_B_SHIFT

| #define CDCE906_Y2_SW_B_SHIFT 0 |

◆ CDCE906_Y3_EN_BYTE

| #define CDCE906_Y3_EN_BYTE 22 |

◆ CDCE906_Y3_EN_MASK

| #define CDCE906_Y3_EN_MASK 0x08 |

◆ CDCE906_Y3_EN_SHIFT

| #define CDCE906_Y3_EN_SHIFT 3 |

◆ CDCE906_Y3_POL_BYTE

| #define CDCE906_Y3_POL_BYTE 22 |

◆ CDCE906_Y3_POL_MASK

| #define CDCE906_Y3_POL_MASK 0x40 |

◆ CDCE906_Y3_POL_SHIFT

| #define CDCE906_Y3_POL_SHIFT 6 |

◆ CDCE906_Y3_SLEW_RATE_BYTE

| #define CDCE906_Y3_SLEW_RATE_BYTE 22 |

◆ CDCE906_Y3_SLEW_RATE_MASK

| #define CDCE906_Y3_SLEW_RATE_MASK 0x30 |

◆ CDCE906_Y3_SLEW_RATE_SHIFT

| #define CDCE906_Y3_SLEW_RATE_SHIFT 4 |

◆ CDCE906_Y3_SW_B_BYTE

| #define CDCE906_Y3_SW_B_BYTE 22 |

◆ CDCE906_Y3_SW_B_MASK

| #define CDCE906_Y3_SW_B_MASK 0x07 |

◆ CDCE906_Y3_SW_B_SHIFT

| #define CDCE906_Y3_SW_B_SHIFT 0 |

◆ CDCE906_Y4_EN_BYTE

| #define CDCE906_Y4_EN_BYTE 23 |

◆ CDCE906_Y4_EN_MASK

| #define CDCE906_Y4_EN_MASK 0x08 |

◆ CDCE906_Y4_EN_SHIFT

| #define CDCE906_Y4_EN_SHIFT 3 |

◆ CDCE906_Y4_POL_BYTE

| #define CDCE906_Y4_POL_BYTE 23 |

◆ CDCE906_Y4_POL_MASK

| #define CDCE906_Y4_POL_MASK 0x40 |

◆ CDCE906_Y4_POL_SHIFT

| #define CDCE906_Y4_POL_SHIFT 6 |

◆ CDCE906_Y4_SLEW_RATE_BYTE

| #define CDCE906_Y4_SLEW_RATE_BYTE 23 |

◆ CDCE906_Y4_SLEW_RATE_MASK

| #define CDCE906_Y4_SLEW_RATE_MASK 0x30 |

◆ CDCE906_Y4_SLEW_RATE_SHIFT

| #define CDCE906_Y4_SLEW_RATE_SHIFT 4 |

◆ CDCE906_Y4_SW_B_BYTE

| #define CDCE906_Y4_SW_B_BYTE 23 |

◆ CDCE906_Y4_SW_B_MASK

| #define CDCE906_Y4_SW_B_MASK 0x07 |

◆ CDCE906_Y4_SW_B_SHIFT

| #define CDCE906_Y4_SW_B_SHIFT 0 |

◆ CDCE906_Y5_EN_BYTE

| #define CDCE906_Y5_EN_BYTE 24 |

◆ CDCE906_Y5_EN_MASK

| #define CDCE906_Y5_EN_MASK 0x08 |

◆ CDCE906_Y5_EN_SHIFT

| #define CDCE906_Y5_EN_SHIFT 3 |

◆ CDCE906_Y5_POL_BYTE

| #define CDCE906_Y5_POL_BYTE 24 |

◆ CDCE906_Y5_POL_MASK

| #define CDCE906_Y5_POL_MASK 0x40 |

◆ CDCE906_Y5_POL_SHIFT

| #define CDCE906_Y5_POL_SHIFT 6 |

◆ CDCE906_Y5_SLEW_RATE_BYTE

| #define CDCE906_Y5_SLEW_RATE_BYTE 24 |

◆ CDCE906_Y5_SLEW_RATE_MASK

| #define CDCE906_Y5_SLEW_RATE_MASK 0x30 |

◆ CDCE906_Y5_SLEW_RATE_SHIFT

| #define CDCE906_Y5_SLEW_RATE_SHIFT 4 |

◆ CDCE906_Y5_SW_B_BYTE

| #define CDCE906_Y5_SW_B_BYTE 24 |

◆ CDCE906_Y5_SW_B_MASK

| #define CDCE906_Y5_SW_B_MASK 0x07 |

◆ CDCE906_Y5_SW_B_SHIFT

| #define CDCE906_Y5_SW_B_SHIFT 0 |

Enumeration Type Documentation

◆ cdce906_clkin_src

| enum cdce906_clkin_src |