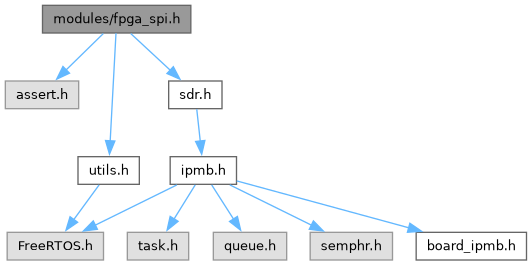

#include <assert.h>

#include "sdr.h"

#include "utils.h"

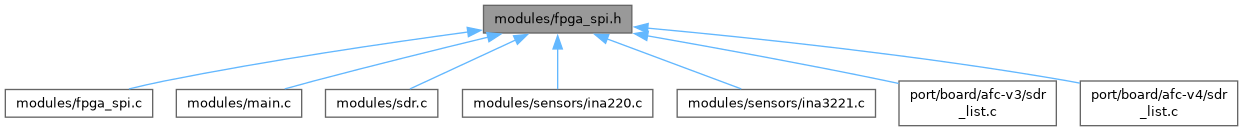

Go to the source code of this file.

◆ DCDC_TEMP_DEVID

| #define DCDC_TEMP_DEVID 0x04 |

◆ FMC1_12V_CURR_DEVID

| #define FMC1_12V_CURR_DEVID 0x06 |

◆ FMC1_12V_DEVID

| #define FMC1_12V_DEVID 0x0C |

◆ FMC1_P3V3_CURR_DEVID

| #define FMC1_P3V3_CURR_DEVID 0x07 |

◆ FMC1_P3V3_DEVID

| #define FMC1_P3V3_DEVID 0x0D |

◆ FMC1_TEMP_DEVID

| #define FMC1_TEMP_DEVID 0x02 |

◆ FMC1_VADJ_CURR_DEVID

| #define FMC1_VADJ_CURR_DEVID 0x08 |

◆ FMC1_VADJ_DEVID

| #define FMC1_VADJ_DEVID 0x0E |

◆ FMC2_12V_CURR_DEVID

| #define FMC2_12V_CURR_DEVID 0x09 |

◆ FMC2_12V_DEVID

| #define FMC2_12V_DEVID 0x0F |

◆ FMC2_P3V3_CURR_DEVID

| #define FMC2_P3V3_CURR_DEVID 0x0A |

◆ FMC2_P3V3_DEVID

| #define FMC2_P3V3_DEVID 0x10 |

◆ FMC2_TEMP_DEVID

| #define FMC2_TEMP_DEVID 0x03 |

◆ FMC2_VADJ_CURR_DEVID

| #define FMC2_VADJ_CURR_DEVID 0x0B |

◆ FMC2_VADJ_DEVID

| #define FMC2_VADJ_DEVID 0x11 |

◆ FPGA_MEM_ADDR_MAX

| #define FPGA_MEM_ADDR_MAX 0xFF |

◆ FPGA_TEMP_DEVID

| #define FPGA_TEMP_DEVID 0x01 |

◆ FPGA_UPDATE_RATE

| #define FPGA_UPDATE_RATE 5000 |

◆ NO_DIAG

◆ RAM_TEMP_DEVID

| #define RAM_TEMP_DEVID 0x05 |

◆ RD_COMMAND

◆ WR_COMMAND

◆ __attribute__() [1/2]

| struct __attribute__ |

( |

(__packed__) | | ) |

|

◆ __attribute__() [2/2]

| struct __attribute__ |

( |

(__packed__, aligned(4)) | | ) |

|

AFC diagnostic struct sent to FPGA via SPI.

◆ fpga_spi_init()

| void fpga_spi_init |

( |

void | | ) |

|

Initializes the FPGA Diagnostics Task.

◆ vTaskFPGA_COMM()

| void vTaskFPGA_COMM |

( |

void * | Parameters | ) |

|

FPGA Diagnostics Task.

This task formats all sensors information and sends to the FPGA via SPI. All the information is accessed by the FPGA using the Wishbone stream.

- Parameters

-

| Parameters | Pointer to parameters passed to the task upon initialization. |

◆ board_diagnostic_t

◆ fmc_diag_t

◆ sensor_diag_t