Type definitions for the System Control Block Registers. More...

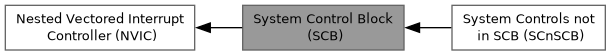

Topics | |

| System Controls not in SCB (SCnSCB) | |

| Type definitions for the System Control and ID Register not in the SCB. | |

Detailed Description

Type definitions for the System Control Block Registers.

Macro Definition Documentation

◆ SCB_AIRCR_ENDIANESS_Msk

| #define SCB_AIRCR_ENDIANESS_Msk (1UL << SCB_AIRCR_ENDIANESS_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB AIRCR: ENDIANESS Mask

◆ SCB_AIRCR_ENDIANESS_Pos

| #define SCB_AIRCR_ENDIANESS_Pos 15U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB AIRCR: ENDIANESS Position

◆ SCB_AIRCR_PRIGROUP_Msk

| #define SCB_AIRCR_PRIGROUP_Msk (7UL << SCB_AIRCR_PRIGROUP_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB AIRCR: PRIGROUP Mask

◆ SCB_AIRCR_PRIGROUP_Pos

| #define SCB_AIRCR_PRIGROUP_Pos 8U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB AIRCR: PRIGROUP Position

◆ SCB_AIRCR_SYSRESETREQ_Msk

| #define SCB_AIRCR_SYSRESETREQ_Msk (1UL << SCB_AIRCR_SYSRESETREQ_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB AIRCR: SYSRESETREQ Mask

◆ SCB_AIRCR_SYSRESETREQ_Pos

| #define SCB_AIRCR_SYSRESETREQ_Pos 2U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB AIRCR: SYSRESETREQ Position

◆ SCB_AIRCR_VECTCLRACTIVE_Msk

| #define SCB_AIRCR_VECTCLRACTIVE_Msk (1UL << SCB_AIRCR_VECTCLRACTIVE_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB AIRCR: VECTCLRACTIVE Mask

◆ SCB_AIRCR_VECTCLRACTIVE_Pos

| #define SCB_AIRCR_VECTCLRACTIVE_Pos 1U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB AIRCR: VECTCLRACTIVE Position

◆ SCB_AIRCR_VECTKEY_Msk

| #define SCB_AIRCR_VECTKEY_Msk (0xFFFFUL << SCB_AIRCR_VECTKEY_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB AIRCR: VECTKEY Mask

◆ SCB_AIRCR_VECTKEY_Pos

| #define SCB_AIRCR_VECTKEY_Pos 16U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB AIRCR: VECTKEY Position

◆ SCB_AIRCR_VECTKEYSTAT_Msk

| #define SCB_AIRCR_VECTKEYSTAT_Msk (0xFFFFUL << SCB_AIRCR_VECTKEYSTAT_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB AIRCR: VECTKEYSTAT Mask

◆ SCB_AIRCR_VECTKEYSTAT_Pos

| #define SCB_AIRCR_VECTKEYSTAT_Pos 16U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB AIRCR: VECTKEYSTAT Position

◆ SCB_AIRCR_VECTRESET_Msk

| #define SCB_AIRCR_VECTRESET_Msk (1UL /*<< SCB_AIRCR_VECTRESET_Pos*/) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB AIRCR: VECTRESET Mask

◆ SCB_AIRCR_VECTRESET_Pos

| #define SCB_AIRCR_VECTRESET_Pos 0U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB AIRCR: VECTRESET Position

◆ SCB_CCR_BFHFNMIGN_Msk

| #define SCB_CCR_BFHFNMIGN_Msk (1UL << SCB_CCR_BFHFNMIGN_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CCR: BFHFNMIGN Mask

◆ SCB_CCR_BFHFNMIGN_Pos

| #define SCB_CCR_BFHFNMIGN_Pos 8U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CCR: BFHFNMIGN Position

◆ SCB_CCR_DIV_0_TRP_Msk

| #define SCB_CCR_DIV_0_TRP_Msk (1UL << SCB_CCR_DIV_0_TRP_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CCR: DIV_0_TRP Mask

◆ SCB_CCR_DIV_0_TRP_Pos

| #define SCB_CCR_DIV_0_TRP_Pos 4U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CCR: DIV_0_TRP Position

◆ SCB_CCR_NONBASETHRDENA_Msk

| #define SCB_CCR_NONBASETHRDENA_Msk (1UL /*<< SCB_CCR_NONBASETHRDENA_Pos*/) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CCR: NONBASETHRDENA Mask

◆ SCB_CCR_NONBASETHRDENA_Pos

| #define SCB_CCR_NONBASETHRDENA_Pos 0U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CCR: NONBASETHRDENA Position

◆ SCB_CCR_STKALIGN_Msk

| #define SCB_CCR_STKALIGN_Msk (1UL << SCB_CCR_STKALIGN_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CCR: STKALIGN Mask

◆ SCB_CCR_STKALIGN_Pos

| #define SCB_CCR_STKALIGN_Pos 9U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CCR: STKALIGN Position

◆ SCB_CCR_UNALIGN_TRP_Msk

| #define SCB_CCR_UNALIGN_TRP_Msk (1UL << SCB_CCR_UNALIGN_TRP_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CCR: UNALIGN_TRP Mask

◆ SCB_CCR_UNALIGN_TRP_Pos

| #define SCB_CCR_UNALIGN_TRP_Pos 3U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CCR: UNALIGN_TRP Position

◆ SCB_CCR_USERSETMPEND_Msk

| #define SCB_CCR_USERSETMPEND_Msk (1UL << SCB_CCR_USERSETMPEND_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CCR: USERSETMPEND Mask

◆ SCB_CCR_USERSETMPEND_Pos

| #define SCB_CCR_USERSETMPEND_Pos 1U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CCR: USERSETMPEND Position

◆ SCB_CFSR_BFARVALID_Msk

| #define SCB_CFSR_BFARVALID_Msk (1UL << SCB_CFSR_BFARVALID_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (BFSR): BFARVALID Mask

◆ SCB_CFSR_BFARVALID_Pos

| #define SCB_CFSR_BFARVALID_Pos (SCB_CFSR_BUSFAULTSR_Pos + 7U) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (BFSR): BFARVALID Position

◆ SCB_CFSR_BUSFAULTSR_Msk

| #define SCB_CFSR_BUSFAULTSR_Msk (0xFFUL << SCB_CFSR_BUSFAULTSR_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR: Bus Fault Status Register Mask

◆ SCB_CFSR_BUSFAULTSR_Pos

| #define SCB_CFSR_BUSFAULTSR_Pos 8U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR: Bus Fault Status Register Position

◆ SCB_CFSR_DACCVIOL_Msk

| #define SCB_CFSR_DACCVIOL_Msk (1UL << SCB_CFSR_DACCVIOL_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (MMFSR): DACCVIOL Mask

◆ SCB_CFSR_DACCVIOL_Pos

| #define SCB_CFSR_DACCVIOL_Pos (SCB_SHCSR_MEMFAULTACT_Pos + 1U) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (MMFSR): DACCVIOL Position

◆ SCB_CFSR_DIVBYZERO_Msk

| #define SCB_CFSR_DIVBYZERO_Msk (1UL << SCB_CFSR_DIVBYZERO_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (UFSR): DIVBYZERO Mask

◆ SCB_CFSR_DIVBYZERO_Pos

| #define SCB_CFSR_DIVBYZERO_Pos (SCB_CFSR_USGFAULTSR_Pos + 9U) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (UFSR): DIVBYZERO Position

◆ SCB_CFSR_IACCVIOL_Msk

| #define SCB_CFSR_IACCVIOL_Msk (1UL /*<< SCB_CFSR_IACCVIOL_Pos*/) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (MMFSR): IACCVIOL Mask

◆ SCB_CFSR_IACCVIOL_Pos

| #define SCB_CFSR_IACCVIOL_Pos (SCB_SHCSR_MEMFAULTACT_Pos + 0U) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (MMFSR): IACCVIOL Position

◆ SCB_CFSR_IBUSERR_Msk

| #define SCB_CFSR_IBUSERR_Msk (1UL << SCB_CFSR_IBUSERR_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (BFSR): IBUSERR Mask

◆ SCB_CFSR_IBUSERR_Pos

| #define SCB_CFSR_IBUSERR_Pos (SCB_CFSR_BUSFAULTSR_Pos + 0U) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (BFSR): IBUSERR Position

◆ SCB_CFSR_IMPRECISERR_Msk

| #define SCB_CFSR_IMPRECISERR_Msk (1UL << SCB_CFSR_IMPRECISERR_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (BFSR): IMPRECISERR Mask

◆ SCB_CFSR_IMPRECISERR_Pos

| #define SCB_CFSR_IMPRECISERR_Pos (SCB_CFSR_BUSFAULTSR_Pos + 2U) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (BFSR): IMPRECISERR Position

◆ SCB_CFSR_INVPC_Msk

| #define SCB_CFSR_INVPC_Msk (1UL << SCB_CFSR_INVPC_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (UFSR): INVPC Mask

◆ SCB_CFSR_INVPC_Pos

| #define SCB_CFSR_INVPC_Pos (SCB_CFSR_USGFAULTSR_Pos + 2U) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (UFSR): INVPC Position

◆ SCB_CFSR_INVSTATE_Msk

| #define SCB_CFSR_INVSTATE_Msk (1UL << SCB_CFSR_INVSTATE_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (UFSR): INVSTATE Mask

◆ SCB_CFSR_INVSTATE_Pos

| #define SCB_CFSR_INVSTATE_Pos (SCB_CFSR_USGFAULTSR_Pos + 1U) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (UFSR): INVSTATE Position

◆ SCB_CFSR_MEMFAULTSR_Msk

| #define SCB_CFSR_MEMFAULTSR_Msk (0xFFUL /*<< SCB_CFSR_MEMFAULTSR_Pos*/) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR: Memory Manage Fault Status Register Mask

◆ SCB_CFSR_MEMFAULTSR_Pos

| #define SCB_CFSR_MEMFAULTSR_Pos 0U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR: Memory Manage Fault Status Register Position

◆ SCB_CFSR_MMARVALID_Msk

| #define SCB_CFSR_MMARVALID_Msk (1UL << SCB_CFSR_MMARVALID_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (MMFSR): MMARVALID Mask

◆ SCB_CFSR_MMARVALID_Pos

| #define SCB_CFSR_MMARVALID_Pos (SCB_SHCSR_MEMFAULTACT_Pos + 7U) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (MMFSR): MMARVALID Position

◆ SCB_CFSR_MSTKERR_Msk

| #define SCB_CFSR_MSTKERR_Msk (1UL << SCB_CFSR_MSTKERR_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (MMFSR): MSTKERR Mask

◆ SCB_CFSR_MSTKERR_Pos

| #define SCB_CFSR_MSTKERR_Pos (SCB_SHCSR_MEMFAULTACT_Pos + 4U) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (MMFSR): MSTKERR Position

◆ SCB_CFSR_MUNSTKERR_Msk

| #define SCB_CFSR_MUNSTKERR_Msk (1UL << SCB_CFSR_MUNSTKERR_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (MMFSR): MUNSTKERR Mask

◆ SCB_CFSR_MUNSTKERR_Pos

| #define SCB_CFSR_MUNSTKERR_Pos (SCB_SHCSR_MEMFAULTACT_Pos + 3U) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (MMFSR): MUNSTKERR Position

◆ SCB_CFSR_NOCP_Msk

| #define SCB_CFSR_NOCP_Msk (1UL << SCB_CFSR_NOCP_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (UFSR): NOCP Mask

◆ SCB_CFSR_NOCP_Pos

| #define SCB_CFSR_NOCP_Pos (SCB_CFSR_USGFAULTSR_Pos + 3U) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (UFSR): NOCP Position

◆ SCB_CFSR_PRECISERR_Msk

| #define SCB_CFSR_PRECISERR_Msk (1UL << SCB_CFSR_PRECISERR_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (BFSR): PRECISERR Mask

◆ SCB_CFSR_PRECISERR_Pos

| #define SCB_CFSR_PRECISERR_Pos (SCB_CFSR_BUSFAULTSR_Pos + 1U) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (BFSR): PRECISERR Position

◆ SCB_CFSR_STKERR_Msk

| #define SCB_CFSR_STKERR_Msk (1UL << SCB_CFSR_STKERR_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (BFSR): STKERR Mask

◆ SCB_CFSR_STKERR_Pos

| #define SCB_CFSR_STKERR_Pos (SCB_CFSR_BUSFAULTSR_Pos + 4U) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (BFSR): STKERR Position

◆ SCB_CFSR_UNALIGNED_Msk

| #define SCB_CFSR_UNALIGNED_Msk (1UL << SCB_CFSR_UNALIGNED_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (UFSR): UNALIGNED Mask

◆ SCB_CFSR_UNALIGNED_Pos

| #define SCB_CFSR_UNALIGNED_Pos (SCB_CFSR_USGFAULTSR_Pos + 8U) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (UFSR): UNALIGNED Position

◆ SCB_CFSR_UNDEFINSTR_Msk

| #define SCB_CFSR_UNDEFINSTR_Msk (1UL << SCB_CFSR_UNDEFINSTR_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (UFSR): UNDEFINSTR Mask

◆ SCB_CFSR_UNDEFINSTR_Pos

| #define SCB_CFSR_UNDEFINSTR_Pos (SCB_CFSR_USGFAULTSR_Pos + 0U) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (UFSR): UNDEFINSTR Position

◆ SCB_CFSR_UNSTKERR_Msk

| #define SCB_CFSR_UNSTKERR_Msk (1UL << SCB_CFSR_UNSTKERR_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (BFSR): UNSTKERR Mask

◆ SCB_CFSR_UNSTKERR_Pos

| #define SCB_CFSR_UNSTKERR_Pos (SCB_CFSR_BUSFAULTSR_Pos + 3U) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR (BFSR): UNSTKERR Position

◆ SCB_CFSR_USGFAULTSR_Msk

| #define SCB_CFSR_USGFAULTSR_Msk (0xFFFFUL << SCB_CFSR_USGFAULTSR_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR: Usage Fault Status Register Mask

◆ SCB_CFSR_USGFAULTSR_Pos

| #define SCB_CFSR_USGFAULTSR_Pos 16U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CFSR: Usage Fault Status Register Position

◆ SCB_CPUID_ARCHITECTURE_Msk

| #define SCB_CPUID_ARCHITECTURE_Msk (0xFUL << SCB_CPUID_ARCHITECTURE_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CPUID: ARCHITECTURE Mask

◆ SCB_CPUID_ARCHITECTURE_Pos

| #define SCB_CPUID_ARCHITECTURE_Pos 16U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CPUID: ARCHITECTURE Position

◆ SCB_CPUID_IMPLEMENTER_Msk

| #define SCB_CPUID_IMPLEMENTER_Msk (0xFFUL << SCB_CPUID_IMPLEMENTER_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CPUID: IMPLEMENTER Mask

◆ SCB_CPUID_IMPLEMENTER_Pos

| #define SCB_CPUID_IMPLEMENTER_Pos 24U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CPUID: IMPLEMENTER Position

◆ SCB_CPUID_PARTNO_Msk

| #define SCB_CPUID_PARTNO_Msk (0xFFFUL << SCB_CPUID_PARTNO_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CPUID: PARTNO Mask

◆ SCB_CPUID_PARTNO_Pos

| #define SCB_CPUID_PARTNO_Pos 4U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CPUID: PARTNO Position

◆ SCB_CPUID_REVISION_Msk

| #define SCB_CPUID_REVISION_Msk (0xFUL /*<< SCB_CPUID_REVISION_Pos*/) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CPUID: REVISION Mask

◆ SCB_CPUID_REVISION_Pos

| #define SCB_CPUID_REVISION_Pos 0U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CPUID: REVISION Position

◆ SCB_CPUID_VARIANT_Msk

| #define SCB_CPUID_VARIANT_Msk (0xFUL << SCB_CPUID_VARIANT_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CPUID: VARIANT Mask

◆ SCB_CPUID_VARIANT_Pos

| #define SCB_CPUID_VARIANT_Pos 20U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB CPUID: VARIANT Position

◆ SCB_DFSR_BKPT_Msk

| #define SCB_DFSR_BKPT_Msk (1UL << SCB_DFSR_BKPT_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB DFSR: BKPT Mask

◆ SCB_DFSR_BKPT_Pos

| #define SCB_DFSR_BKPT_Pos 1U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB DFSR: BKPT Position

◆ SCB_DFSR_DWTTRAP_Msk

| #define SCB_DFSR_DWTTRAP_Msk (1UL << SCB_DFSR_DWTTRAP_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB DFSR: DWTTRAP Mask

◆ SCB_DFSR_DWTTRAP_Pos

| #define SCB_DFSR_DWTTRAP_Pos 2U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB DFSR: DWTTRAP Position

◆ SCB_DFSR_EXTERNAL_Msk

| #define SCB_DFSR_EXTERNAL_Msk (1UL << SCB_DFSR_EXTERNAL_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB DFSR: EXTERNAL Mask

◆ SCB_DFSR_EXTERNAL_Pos

| #define SCB_DFSR_EXTERNAL_Pos 4U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB DFSR: EXTERNAL Position

◆ SCB_DFSR_HALTED_Msk

| #define SCB_DFSR_HALTED_Msk (1UL /*<< SCB_DFSR_HALTED_Pos*/) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB DFSR: HALTED Mask

◆ SCB_DFSR_HALTED_Pos

| #define SCB_DFSR_HALTED_Pos 0U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB DFSR: HALTED Position

◆ SCB_DFSR_VCATCH_Msk

| #define SCB_DFSR_VCATCH_Msk (1UL << SCB_DFSR_VCATCH_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB DFSR: VCATCH Mask

◆ SCB_DFSR_VCATCH_Pos

| #define SCB_DFSR_VCATCH_Pos 3U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB DFSR: VCATCH Position

◆ SCB_HFSR_DEBUGEVT_Msk

| #define SCB_HFSR_DEBUGEVT_Msk (1UL << SCB_HFSR_DEBUGEVT_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB HFSR: DEBUGEVT Mask

◆ SCB_HFSR_DEBUGEVT_Pos

| #define SCB_HFSR_DEBUGEVT_Pos 31U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB HFSR: DEBUGEVT Position

◆ SCB_HFSR_FORCED_Msk

| #define SCB_HFSR_FORCED_Msk (1UL << SCB_HFSR_FORCED_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB HFSR: FORCED Mask

◆ SCB_HFSR_FORCED_Pos

| #define SCB_HFSR_FORCED_Pos 30U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB HFSR: FORCED Position

◆ SCB_HFSR_VECTTBL_Msk

| #define SCB_HFSR_VECTTBL_Msk (1UL << SCB_HFSR_VECTTBL_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB HFSR: VECTTBL Mask

◆ SCB_HFSR_VECTTBL_Pos

| #define SCB_HFSR_VECTTBL_Pos 1U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB HFSR: VECTTBL Position

◆ SCB_ICSR_ISRPENDING_Msk

| #define SCB_ICSR_ISRPENDING_Msk (1UL << SCB_ICSR_ISRPENDING_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB ICSR: ISRPENDING Mask

◆ SCB_ICSR_ISRPENDING_Pos

| #define SCB_ICSR_ISRPENDING_Pos 22U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB ICSR: ISRPENDING Position

◆ SCB_ICSR_ISRPREEMPT_Msk

| #define SCB_ICSR_ISRPREEMPT_Msk (1UL << SCB_ICSR_ISRPREEMPT_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB ICSR: ISRPREEMPT Mask

◆ SCB_ICSR_ISRPREEMPT_Pos

| #define SCB_ICSR_ISRPREEMPT_Pos 23U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB ICSR: ISRPREEMPT Position

◆ SCB_ICSR_NMIPENDSET_Msk

| #define SCB_ICSR_NMIPENDSET_Msk (1UL << SCB_ICSR_NMIPENDSET_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB ICSR: NMIPENDSET Mask

◆ SCB_ICSR_NMIPENDSET_Pos

| #define SCB_ICSR_NMIPENDSET_Pos 31U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB ICSR: NMIPENDSET Position

◆ SCB_ICSR_PENDSTCLR_Msk

| #define SCB_ICSR_PENDSTCLR_Msk (1UL << SCB_ICSR_PENDSTCLR_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB ICSR: PENDSTCLR Mask

◆ SCB_ICSR_PENDSTCLR_Pos

| #define SCB_ICSR_PENDSTCLR_Pos 25U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB ICSR: PENDSTCLR Position

◆ SCB_ICSR_PENDSTSET_Msk

| #define SCB_ICSR_PENDSTSET_Msk (1UL << SCB_ICSR_PENDSTSET_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB ICSR: PENDSTSET Mask

◆ SCB_ICSR_PENDSTSET_Pos

| #define SCB_ICSR_PENDSTSET_Pos 26U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB ICSR: PENDSTSET Position

◆ SCB_ICSR_PENDSVCLR_Msk

| #define SCB_ICSR_PENDSVCLR_Msk (1UL << SCB_ICSR_PENDSVCLR_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB ICSR: PENDSVCLR Mask

◆ SCB_ICSR_PENDSVCLR_Pos

| #define SCB_ICSR_PENDSVCLR_Pos 27U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB ICSR: PENDSVCLR Position

◆ SCB_ICSR_PENDSVSET_Msk

| #define SCB_ICSR_PENDSVSET_Msk (1UL << SCB_ICSR_PENDSVSET_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB ICSR: PENDSVSET Mask

◆ SCB_ICSR_PENDSVSET_Pos

| #define SCB_ICSR_PENDSVSET_Pos 28U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB ICSR: PENDSVSET Position

◆ SCB_ICSR_RETTOBASE_Msk

| #define SCB_ICSR_RETTOBASE_Msk (1UL << SCB_ICSR_RETTOBASE_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB ICSR: RETTOBASE Mask

◆ SCB_ICSR_RETTOBASE_Pos

| #define SCB_ICSR_RETTOBASE_Pos 11U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB ICSR: RETTOBASE Position

◆ SCB_ICSR_VECTACTIVE_Msk

| #define SCB_ICSR_VECTACTIVE_Msk (0x1FFUL /*<< SCB_ICSR_VECTACTIVE_Pos*/) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB ICSR: VECTACTIVE Mask

◆ SCB_ICSR_VECTACTIVE_Pos

| #define SCB_ICSR_VECTACTIVE_Pos 0U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB ICSR: VECTACTIVE Position

◆ SCB_ICSR_VECTPENDING_Msk

| #define SCB_ICSR_VECTPENDING_Msk (0x1FFUL << SCB_ICSR_VECTPENDING_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB ICSR: VECTPENDING Mask

◆ SCB_ICSR_VECTPENDING_Pos

| #define SCB_ICSR_VECTPENDING_Pos 12U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB ICSR: VECTPENDING Position

◆ SCB_SCR_SEVONPEND_Msk

| #define SCB_SCR_SEVONPEND_Msk (1UL << SCB_SCR_SEVONPEND_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SCR: SEVONPEND Mask

◆ SCB_SCR_SEVONPEND_Pos

| #define SCB_SCR_SEVONPEND_Pos 4U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SCR: SEVONPEND Position

◆ SCB_SCR_SLEEPDEEP_Msk

| #define SCB_SCR_SLEEPDEEP_Msk (1UL << SCB_SCR_SLEEPDEEP_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SCR: SLEEPDEEP Mask

◆ SCB_SCR_SLEEPDEEP_Pos

| #define SCB_SCR_SLEEPDEEP_Pos 2U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SCR: SLEEPDEEP Position

◆ SCB_SCR_SLEEPONEXIT_Msk

| #define SCB_SCR_SLEEPONEXIT_Msk (1UL << SCB_SCR_SLEEPONEXIT_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SCR: SLEEPONEXIT Mask

◆ SCB_SCR_SLEEPONEXIT_Pos

| #define SCB_SCR_SLEEPONEXIT_Pos 1U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SCR: SLEEPONEXIT Position

◆ SCB_SHCSR_BUSFAULTACT_Msk

| #define SCB_SHCSR_BUSFAULTACT_Msk (1UL << SCB_SHCSR_BUSFAULTACT_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: BUSFAULTACT Mask

◆ SCB_SHCSR_BUSFAULTACT_Pos

| #define SCB_SHCSR_BUSFAULTACT_Pos 1U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: BUSFAULTACT Position

◆ SCB_SHCSR_BUSFAULTENA_Msk

| #define SCB_SHCSR_BUSFAULTENA_Msk (1UL << SCB_SHCSR_BUSFAULTENA_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: BUSFAULTENA Mask

◆ SCB_SHCSR_BUSFAULTENA_Pos

| #define SCB_SHCSR_BUSFAULTENA_Pos 17U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: BUSFAULTENA Position

◆ SCB_SHCSR_BUSFAULTPENDED_Msk

| #define SCB_SHCSR_BUSFAULTPENDED_Msk (1UL << SCB_SHCSR_BUSFAULTPENDED_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: BUSFAULTPENDED Mask

◆ SCB_SHCSR_BUSFAULTPENDED_Pos

| #define SCB_SHCSR_BUSFAULTPENDED_Pos 14U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: BUSFAULTPENDED Position

◆ SCB_SHCSR_MEMFAULTACT_Msk

| #define SCB_SHCSR_MEMFAULTACT_Msk (1UL /*<< SCB_SHCSR_MEMFAULTACT_Pos*/) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: MEMFAULTACT Mask

◆ SCB_SHCSR_MEMFAULTACT_Pos

| #define SCB_SHCSR_MEMFAULTACT_Pos 0U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: MEMFAULTACT Position

◆ SCB_SHCSR_MEMFAULTENA_Msk

| #define SCB_SHCSR_MEMFAULTENA_Msk (1UL << SCB_SHCSR_MEMFAULTENA_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: MEMFAULTENA Mask

◆ SCB_SHCSR_MEMFAULTENA_Pos

| #define SCB_SHCSR_MEMFAULTENA_Pos 16U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: MEMFAULTENA Position

◆ SCB_SHCSR_MEMFAULTPENDED_Msk

| #define SCB_SHCSR_MEMFAULTPENDED_Msk (1UL << SCB_SHCSR_MEMFAULTPENDED_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: MEMFAULTPENDED Mask

◆ SCB_SHCSR_MEMFAULTPENDED_Pos

| #define SCB_SHCSR_MEMFAULTPENDED_Pos 13U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: MEMFAULTPENDED Position

◆ SCB_SHCSR_MONITORACT_Msk

| #define SCB_SHCSR_MONITORACT_Msk (1UL << SCB_SHCSR_MONITORACT_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: MONITORACT Mask

◆ SCB_SHCSR_MONITORACT_Pos

| #define SCB_SHCSR_MONITORACT_Pos 8U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: MONITORACT Position

◆ SCB_SHCSR_PENDSVACT_Msk

| #define SCB_SHCSR_PENDSVACT_Msk (1UL << SCB_SHCSR_PENDSVACT_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: PENDSVACT Mask

◆ SCB_SHCSR_PENDSVACT_Pos

| #define SCB_SHCSR_PENDSVACT_Pos 10U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: PENDSVACT Position

◆ SCB_SHCSR_SVCALLACT_Msk

| #define SCB_SHCSR_SVCALLACT_Msk (1UL << SCB_SHCSR_SVCALLACT_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: SVCALLACT Mask

◆ SCB_SHCSR_SVCALLACT_Pos

| #define SCB_SHCSR_SVCALLACT_Pos 7U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: SVCALLACT Position

◆ SCB_SHCSR_SVCALLPENDED_Msk

| #define SCB_SHCSR_SVCALLPENDED_Msk (1UL << SCB_SHCSR_SVCALLPENDED_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: SVCALLPENDED Mask

◆ SCB_SHCSR_SVCALLPENDED_Pos

| #define SCB_SHCSR_SVCALLPENDED_Pos 15U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: SVCALLPENDED Position

◆ SCB_SHCSR_SYSTICKACT_Msk

| #define SCB_SHCSR_SYSTICKACT_Msk (1UL << SCB_SHCSR_SYSTICKACT_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: SYSTICKACT Mask

◆ SCB_SHCSR_SYSTICKACT_Pos

| #define SCB_SHCSR_SYSTICKACT_Pos 11U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: SYSTICKACT Position

◆ SCB_SHCSR_USGFAULTACT_Msk

| #define SCB_SHCSR_USGFAULTACT_Msk (1UL << SCB_SHCSR_USGFAULTACT_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: USGFAULTACT Mask

◆ SCB_SHCSR_USGFAULTACT_Pos

| #define SCB_SHCSR_USGFAULTACT_Pos 3U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: USGFAULTACT Position

◆ SCB_SHCSR_USGFAULTENA_Msk

| #define SCB_SHCSR_USGFAULTENA_Msk (1UL << SCB_SHCSR_USGFAULTENA_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: USGFAULTENA Mask

◆ SCB_SHCSR_USGFAULTENA_Pos

| #define SCB_SHCSR_USGFAULTENA_Pos 18U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: USGFAULTENA Position

◆ SCB_SHCSR_USGFAULTPENDED_Msk

| #define SCB_SHCSR_USGFAULTPENDED_Msk (1UL << SCB_SHCSR_USGFAULTPENDED_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: USGFAULTPENDED Mask

◆ SCB_SHCSR_USGFAULTPENDED_Pos

| #define SCB_SHCSR_USGFAULTPENDED_Pos 12U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB SHCSR: USGFAULTPENDED Position

◆ SCB_VTOR_TBLOFF_Msk

| #define SCB_VTOR_TBLOFF_Msk (0x1FFFFFFUL << SCB_VTOR_TBLOFF_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB VTOR: TBLOFF Mask

◆ SCB_VTOR_TBLOFF_Pos

| #define SCB_VTOR_TBLOFF_Pos 7U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

SCB VTOR: TBLOFF Position