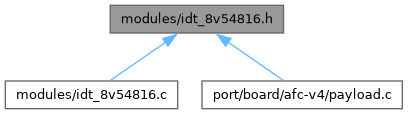

Go to the source code of this file.

|

| enum | IDT_CLK_SRC {

IDT_SRC_CH0

, IDT_SRC_CH1

, IDT_SRC_CH2

, IDT_SRC_CH3

,

IDT_SRC_CH4

, IDT_SRC_CH5

, IDT_SRC_CH6

, IDT_SRC_CH7

,

IDT_SRC_CH8

, IDT_SRC_CH9

, IDT_SRC_CH10

, IDT_SRC_CH11

,

IDT_SRC_CH12

, IDT_SRC_CH13

, IDT_SRC_CH14

, IDT_SRC_CH15

} |

| |

◆ IDT_DIR_IN

◆ IDT_DIR_OUT

◆ IDT_MASK_DIR

| #define IDT_MASK_DIR 1<<7 |

◆ IDT_MASK_POL

| #define IDT_MASK_POL 1<<5 |

◆ IDT_MASK_SRC

◆ IDT_MASK_TERM

| #define IDT_MASK_TERM 1<<6 |

◆ IDT_POL_N

◆ IDT_POL_P

◆ IDT_TERM_OFF

◆ IDT_TERM_ON

◆ IDT_CLK_SRC

| Enumerator |

|---|

| IDT_SRC_CH0 | |

| IDT_SRC_CH1 | |

| IDT_SRC_CH2 | |

| IDT_SRC_CH3 | |

| IDT_SRC_CH4 | |

| IDT_SRC_CH5 | |

| IDT_SRC_CH6 | |

| IDT_SRC_CH7 | |

| IDT_SRC_CH8 | |

| IDT_SRC_CH9 | |

| IDT_SRC_CH10 | |

| IDT_SRC_CH11 | |

| IDT_SRC_CH12 | |

| IDT_SRC_CH13 | |

| IDT_SRC_CH14 | |

| IDT_SRC_CH15 | |

◆ clock_switch_default_config()

| uint8_t clock_switch_default_config |

( |

| ) |

|

◆ clock_switch_read_reg()

| uint8_t clock_switch_read_reg |

( |

uint8_t * | rx_data | ) |

|

◆ clock_switch_read_single_channel()

| uint8_t clock_switch_read_single_channel |

( |

uint8_t | channel, |

|

|

uint8_t * | data ) |

◆ clock_switch_set_single_channel()

| uint8_t clock_switch_set_single_channel |

( |

uint8_t | channel, |

|

|

uint8_t | value ) |

◆ clock_switch_write_reg()

| uint8_t clock_switch_write_reg |

( |

uint8_t * | tx_data | ) |

|