Loading...

Searching...

No Matches

pin_mapping.h File Reference

Hardware pin definitions for AFCv4.0. More...

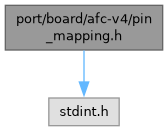

#include <stdint.h>

Include dependency graph for pin_mapping.h:

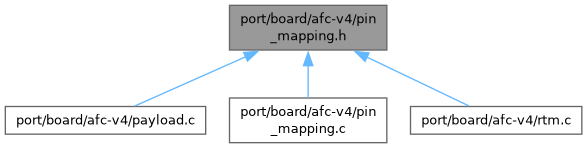

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Data Structures | |

| struct | external_gpio |

Macros | |

| #define | FPGA_SPI 0 |

| #define | UART_DEBUG 0 |

| #define | I2C0_SDA PIN_DEF( PORT0, 27, (IOCON_FUNC1 | IOCON_MODE_INACT), NON_GPIO ) |

| #define | I2C0_SCL PIN_DEF( PORT0, 28, (IOCON_FUNC1 | IOCON_MODE_INACT), NON_GPIO ) |

| #define | I2C1_SDA PIN_DEF( PORT0, 0, (IOCON_FUNC3 | IOCON_MODE_INACT), NON_GPIO ) |

| #define | I2C1_SCL PIN_DEF( PORT0, 1, (IOCON_FUNC3 | IOCON_MODE_INACT), NON_GPIO ) |

| #define | I2C2_SDA PIN_DEF( PORT0, 10, (IOCON_FUNC2 | IOCON_MODE_INACT), NON_GPIO ) |

| #define | I2C2_SCL PIN_DEF( PORT0, 11, (IOCON_FUNC2 | IOCON_MODE_INACT), NON_GPIO ) |

| #define | UART_DEBUG_TXD PIN_DEF( PORT0, 2, (IOCON_FUNC1 | IOCON_MODE_INACT), NON_GPIO ) |

| #define | UART_DEBUG_RXD PIN_DEF( PORT0, 3, (IOCON_FUNC1 | IOCON_MODE_INACT), NON_GPIO ) |

| #define | SSP0_SCK PIN_DEF( PORT1, 20, (IOCON_FUNC3 | IOCON_MODE_INACT), NON_GPIO ) |

| #define | SSP0_SSEL PIN_DEF( PORT1, 21, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_OUTPUT ) |

| #define | SSP0_MISO PIN_DEF( PORT1, 23, (IOCON_FUNC3 | IOCON_MODE_INACT), NON_GPIO ) |

| #define | SSP0_MOSI PIN_DEF( PORT1, 24, (IOCON_FUNC3 | IOCON_MODE_INACT), NON_GPIO ) |

| #define | SPI_SCK PIN_DEF( PORT0, 15, (IOCON_FUNC3 | IOCON_MODE_INACT), NON_GPIO ) |

| #define | SPI_SSEL PIN_DEF( PORT0, 16, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_OUTPUT ) |

| #define | SPI_MOSI PIN_DEF( PORT0, 18, (IOCON_FUNC3 | IOCON_MODE_INACT), NON_GPIO ) |

| #define | TRACEDATA3 PIN_DEF( PORT2, 2, (IOCON_FUNC3 | IOCON_MODE_INACT), NON_GPIO ) |

| #define | TRACEDATA2 PIN_DEF( PORT2, 3, (IOCON_FUNC3 | IOCON_MODE_INACT), NON_GPIO ) |

| #define | TRACEDATA1 PIN_DEF( PORT2, 4, (IOCON_FUNC3 | IOCON_MODE_INACT), NON_GPIO ) |

| #define | TRACEDATA0 PIN_DEF( PORT2, 5, (IOCON_FUNC3 | IOCON_MODE_INACT), NON_GPIO ) |

| #define | TRACECLK PIN_DEF( PORT2, 6, (IOCON_FUNC3 | IOCON_MODE_INACT), NON_GPIO ) |

| #define | ADC_PAYLOAD_DETECTOR PIN_DEF( PORT0, 24, (IOCON_FUNC1 | IOCON_MODE_INACT), NON_GPIO ) |

| #define | GPIO_I2C_MUX_ADDR1 PIN_DEF( PORT0, 4, (IOCON_FUNC0 | IOCON_MODE_PULLDOWN), GPIO_DIR_OUTPUT ) |

| #define | GPIO_I2C_MUX_ADDR2 PIN_DEF( PORT0, 5, (IOCON_FUNC0 | IOCON_MODE_PULLDOWN), GPIO_DIR_OUTPUT ) |

| #define | GPIO_I2C_SW_RESETn PIN_DEF( PORT0, 19, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_OUTPUT ) |

| #define | GPIO_RTS PIN_DEF( PORT2, 10, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_PG_RESETn PIN_DEF( PORT1, 22, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_PGOOD_P1V0 PIN_DEF( PORT3, 26, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_AMC_RTM_CRITICAL PIN_DEF( PORT1, 26, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_AMC_RTM_TC PIN_DEF( PORT1, 28, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_AMC_RTM_WARNING PIN_DEF( PORT1, 29, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_AMC_RTM_PV PIN_DEF( PORT1, 27, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_FMC1_PG_M2C PIN_DEF( PORT1, 16, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_FMC2_PG_M2C PIN_DEF( PORT1, 17, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_FMC1_PG_C2M PIN_DEF( PORT1, 18, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_OUTPUT ) |

| #define | GPIO_FMC2_PG_C2M PIN_DEF( PORT1, 19, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_OUTPUT ) |

| #define | GPIO_FMC1_CRITICAL PIN_DEF( PORT0, 23, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_FMC1_TC PIN_DEF( PORT0, 25, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_FMC1_WARNING PIN_DEF( PORT0, 26, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_FMC1_PV PIN_DEF( PORT1, 31, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_FMC2_CRITICAL PIN_DEF( PORT2, 7, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_FMC2_TC PIN_DEF( PORT4, 28, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_FMC2_WARNING PIN_DEF( PORT4, 29, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_FMC2_PV PIN_DEF( PORT3, 25, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_GA0 PIN_DEF( PORT1, 0, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_GA1 PIN_DEF( PORT1, 1, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_GA2 PIN_DEF( PORT1, 4, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_GA_TEST PIN_DEF( PORT1, 8, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_OUTPUT ) |

| #define | GPIO_LEDBLUE PIN_DEF( PORT1, 9, (IOCON_FUNC0 | IOCON_MODE_PULLUP), GPIO_DIR_OUTPUT ) |

| #define | GPIO_LEDGREEN PIN_DEF( PORT1, 10, (IOCON_FUNC0 | IOCON_MODE_PULLDOWN), GPIO_DIR_OUTPUT ) |

| #define | GPIO_LEDRED PIN_DEF( PORT1, 25, (IOCON_FUNC0 | IOCON_MODE_PULLDOWN), GPIO_DIR_OUTPUT ) |

| #define | GPIO_FRONT_BUTTON PIN_DEF( PORT2, 12, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_HOT_SWAP_HANDLE PIN_DEF( PORT2, 13, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_FPGA_DONE_B PIN_DEF( PORT0, 22, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_FPGA_INITB PIN_DEF( PORT0, 20, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_OUTPUT ) |

| #define | GPIO_FPGA_RESET PIN_DEF( PORT2, 9, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_OUTPUT ) |

| #define | GPIO_DAC_VADJ_RST PIN_DEF( PORT0, 21, (IOCON_FUNC0 | IOCON_MODE_PULLUP), GPIO_DIR_OUTPUT ) |

| #define | GPIO_MMC_ENABLE PIN_DEF( PORT2, 8, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_OVERTEMPn PIN_DEF( PORT2, 11, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_FMC1_JTAG_Override PIN_DEF( PORT2, 1, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_OUTPUT ) |

| #define | GPIO_FMC2_JTAG_Override PIN_DEF( PORT0, 8, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_OUTPUT ) |

| #define | GPIO_RTM_JTAG_Override PIN_DEF( PORT2, 0, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_OUTPUT ) |

| #define | GPIO_EEPROM_WP PIN_DEF( PORT1, 30, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_OUTPUT ) |

| #define | GPIO_CLK_DIR_FMC2 PIN_DEF( PORT0, 6, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_CLK_DIR_FMC1 PIN_DEF( PORT0, 7, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_FMC1_PRSNT_M2C PIN_DEF( PORT1, 14, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_FMC2_PRSNT_M2C PIN_DEF( PORT1, 15, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | GPIO_RTM_PS PIN_DEF( PORT0, 29, (IOCON_FUNC0 | IOCON_MODE_INACT), GPIO_DIR_INPUT ) |

| #define | PIN_CFG_LIST |

Typedefs | |

| typedef struct external_gpio | external_gpio_t |

Variables | |

| const external_gpio_t | ext_gpios [16] |

Detailed Description

Hardware pin definitions for AFCv4.0.

Typedef Documentation

◆ external_gpio_t

| typedef struct external_gpio external_gpio_t |

Enumeration Type Documentation

◆ anonymous enum

| anonymous enum |