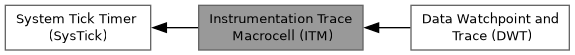

Type definitions for the Instrumentation Trace Macrocell (ITM) More...

Topics | |

| Data Watchpoint and Trace (DWT) | |

| Type definitions for the Data Watchpoint and Trace (DWT) | |

Detailed Description

Type definitions for the Instrumentation Trace Macrocell (ITM)

Macro Definition Documentation

◆ ITM_LSR_Access_Msk

| #define ITM_LSR_Access_Msk (1UL << ITM_LSR_Access_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM LSR: Access Mask

◆ ITM_LSR_Access_Pos

| #define ITM_LSR_Access_Pos 1U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM LSR: Access Position

◆ ITM_LSR_ByteAcc_Msk

| #define ITM_LSR_ByteAcc_Msk (1UL << ITM_LSR_ByteAcc_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM LSR: ByteAcc Mask

◆ ITM_LSR_ByteAcc_Pos

| #define ITM_LSR_ByteAcc_Pos 2U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM LSR: ByteAcc Position

◆ ITM_LSR_Present_Msk

| #define ITM_LSR_Present_Msk (1UL /*<< ITM_LSR_Present_Pos*/) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM LSR: Present Mask

◆ ITM_LSR_Present_Pos

| #define ITM_LSR_Present_Pos 0U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM LSR: Present Position

◆ ITM_TCR_BUSY_Msk

| #define ITM_TCR_BUSY_Msk (1UL << ITM_TCR_BUSY_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM TCR: BUSY Mask

◆ ITM_TCR_BUSY_Pos

| #define ITM_TCR_BUSY_Pos 23U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM TCR: BUSY Position

◆ ITM_TCR_DWTENA_Msk

| #define ITM_TCR_DWTENA_Msk (1UL << ITM_TCR_DWTENA_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM TCR: DWTENA Mask

◆ ITM_TCR_DWTENA_Pos

| #define ITM_TCR_DWTENA_Pos 3U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM TCR: DWTENA Position

◆ ITM_TCR_GTSFREQ_Msk

| #define ITM_TCR_GTSFREQ_Msk (3UL << ITM_TCR_GTSFREQ_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM TCR: Global timestamp frequency Mask

◆ ITM_TCR_GTSFREQ_Pos

| #define ITM_TCR_GTSFREQ_Pos 10U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM TCR: Global timestamp frequency Position

◆ ITM_TCR_ITMENA_Msk

| #define ITM_TCR_ITMENA_Msk (1UL /*<< ITM_TCR_ITMENA_Pos*/) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM TCR: ITM Enable bit Mask

◆ ITM_TCR_ITMENA_Pos

| #define ITM_TCR_ITMENA_Pos 0U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM TCR: ITM Enable bit Position

◆ ITM_TCR_SWOENA_Msk

| #define ITM_TCR_SWOENA_Msk (1UL << ITM_TCR_SWOENA_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM TCR: SWOENA Mask

◆ ITM_TCR_SWOENA_Pos

| #define ITM_TCR_SWOENA_Pos 4U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM TCR: SWOENA Position

◆ ITM_TCR_SYNCENA_Msk

| #define ITM_TCR_SYNCENA_Msk (1UL << ITM_TCR_SYNCENA_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM TCR: SYNCENA Mask

◆ ITM_TCR_SYNCENA_Pos

| #define ITM_TCR_SYNCENA_Pos 2U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM TCR: SYNCENA Position

◆ ITM_TCR_TraceBusID_Msk

| #define ITM_TCR_TraceBusID_Msk (0x7FUL << ITM_TCR_TraceBusID_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM TCR: ATBID Mask

◆ ITM_TCR_TraceBusID_Pos

| #define ITM_TCR_TraceBusID_Pos 16U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM TCR: ATBID Position

◆ ITM_TCR_TSENA_Msk

| #define ITM_TCR_TSENA_Msk (1UL << ITM_TCR_TSENA_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM TCR: TSENA Mask

◆ ITM_TCR_TSENA_Pos

| #define ITM_TCR_TSENA_Pos 1U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM TCR: TSENA Position

◆ ITM_TCR_TSPrescale_Msk

| #define ITM_TCR_TSPrescale_Msk (3UL << ITM_TCR_TSPrescale_Pos) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM TCR: TSPrescale Mask

◆ ITM_TCR_TSPrescale_Pos

| #define ITM_TCR_TSPrescale_Pos 8U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM TCR: TSPrescale Position

◆ ITM_TPR_PRIVMASK_Msk

| #define ITM_TPR_PRIVMASK_Msk (0xFFFFFFFFUL /*<< ITM_TPR_PRIVMASK_Pos*/) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM TPR: PRIVMASK Mask

◆ ITM_TPR_PRIVMASK_Pos

| #define ITM_TPR_PRIVMASK_Pos 0U |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/core_cm3.h>

ITM TPR: PRIVMASK Position