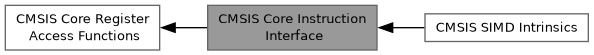

Topics | |

| CMSIS SIMD Intrinsics | |

Macros | |

| #define | __NOP __nop |

| No Operation. | |

| #define | __WFI __wfi |

| Wait For Interrupt. | |

| #define | __WFE __wfe |

| Wait For Event. | |

| #define | __SEV __sev |

| Send Event. | |

| #define | __ISB() |

| Instruction Synchronization Barrier. | |

| #define | __DSB() |

| Data Synchronization Barrier. | |

| #define | __DMB() |

| Data Memory Barrier. | |

| #define | __REV __rev |

| Reverse byte order (32 bit) | |

| #define | __ROR __ror |

| Rotate Right in unsigned value (32 bit) | |

| #define | __BKPT(value) |

| Breakpoint. | |

| #define | __CLZ __clz |

| Count leading zeros. | |

| #define | __CMSIS_GCC_OUT_REG(r) |

| #define | __CMSIS_GCC_RW_REG(r) |

| #define | __CMSIS_GCC_USE_REG(r) |

| #define | __NOP __builtin_arm_nop |

| No Operation. | |

| #define | __WFI __builtin_arm_wfi |

| Wait For Interrupt. | |

| #define | __WFE __builtin_arm_wfe |

| Wait For Event. | |

| #define | __SEV __builtin_arm_sev |

| Send Event. | |

| #define | __ISB() |

| Instruction Synchronization Barrier. | |

| #define | __DSB() |

| Data Synchronization Barrier. | |

| #define | __DMB() |

| Data Memory Barrier. | |

| #define | __REV(value) |

| Reverse byte order (32 bit) | |

| #define | __REV16(value) |

| Reverse byte order (16 bit) | |

| #define | __REVSH(value) |

| Reverse byte order (16 bit) | |

| #define | __BKPT(value) |

| Breakpoint. | |

| #define | __RBIT __builtin_arm_rbit |

| Reverse bit order of value. | |

| #define | __CMSIS_GCC_OUT_REG(r) |

| #define | __CMSIS_GCC_USE_REG(r) |

| #define | __NOP __builtin_arm_nop |

| No Operation. | |

| #define | __WFI __builtin_arm_wfi |

| Wait For Interrupt. | |

| #define | __WFE __builtin_arm_wfe |

| Wait For Event. | |

| #define | __SEV __builtin_arm_sev |

| Send Event. | |

| #define | __ISB() |

| Instruction Synchronization Barrier. | |

| #define | __DSB() |

| Data Synchronization Barrier. | |

| #define | __DMB() |

| Data Memory Barrier. | |

| #define | __REV(value) |

| Reverse byte order (32 bit) | |

| #define | __REV16(value) |

| Reverse byte order (16 bit) | |

| #define | __REVSH(value) |

| Reverse byte order (16 bit) | |

| #define | __BKPT(value) |

| Breakpoint. | |

| #define | __RBIT __builtin_arm_rbit |

| Reverse bit order of value. | |

| #define | __CMSIS_GCC_OUT_REG(r) |

| #define | __CMSIS_GCC_RW_REG(r) |

| #define | __CMSIS_GCC_USE_REG(r) |

| #define | __NOP() |

| No Operation. | |

| #define | __WFI() |

| Wait For Interrupt. | |

| #define | __WFE() |

| Wait For Event. | |

| #define | __SEV() |

| Send Event. | |

| #define | __BKPT(value) |

| Breakpoint. | |

Functions | |

| __attribute__ ((section(".rev16_text"))) __STATIC_INLINE __ASM uint32_t __REV16(uint32_t value) | |

| Reverse byte order (16 bit) | |

| __attribute__ ((section(".revsh_text"))) __STATIC_INLINE __ASM int16_t __REVSH(int16_t value) | |

| Reverse byte order (16 bit) | |

| __attribute__ ((always_inline)) __STATIC_INLINE uint32_t __RBIT(uint32_t value) | |

| Reverse bit order of value. | |

| __STATIC_FORCEINLINE uint32_t | __ROR (uint32_t op1, uint32_t op2) |

| Rotate Right in unsigned value (32 bit) | |

| __STATIC_FORCEINLINE uint8_t | __CLZ (uint32_t value) |

| Count leading zeros. | |

| __STATIC_FORCEINLINE int32_t | __SSAT (int32_t val, uint32_t sat) |

| Signed Saturate. | |

| __STATIC_FORCEINLINE uint32_t | __USAT (int32_t val, uint32_t sat) |

| Unsigned Saturate. | |

| __STATIC_FORCEINLINE void | __ISB (void) |

| Instruction Synchronization Barrier. | |

| __STATIC_FORCEINLINE void | __DSB (void) |

| Data Synchronization Barrier. | |

| __STATIC_FORCEINLINE void | __DMB (void) |

| Data Memory Barrier. | |

| __STATIC_FORCEINLINE uint32_t | __REV (uint32_t value) |

| Reverse byte order (32 bit) | |

| __STATIC_FORCEINLINE uint32_t | __REV16 (uint32_t value) |

| Reverse byte order (16 bit) | |

| __STATIC_FORCEINLINE int16_t | __REVSH (int16_t value) |

| Reverse byte order (16 bit) | |

| __STATIC_FORCEINLINE uint32_t | __RBIT (uint32_t value) |

| Reverse bit order of value. | |

Variables | |

| uint32_t | sat |

Detailed Description

Access to dedicated instructions

Macro Definition Documentation

◆ __BKPT [1/4]

| #define __BKPT | ( | value | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armcc.h>

Breakpoint.

Causes the processor to enter Debug state. Debug tools can use this to investigate system state when the instruction at a particular address is reached.

- Parameters

-

[in] value is ignored by the processor. If required, a debugger can use it to store additional information about the breakpoint.

◆ __BKPT [2/4]

| #define __BKPT | ( | value | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang.h>

Breakpoint.

Causes the processor to enter Debug state. Debug tools can use this to investigate system state when the instruction at a particular address is reached.

- Parameters

-

[in] value is ignored by the processor. If required, a debugger can use it to store additional information about the breakpoint.

◆ __BKPT [3/4]

| #define __BKPT | ( | value | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang_ltm.h>

Breakpoint.

Causes the processor to enter Debug state. Debug tools can use this to investigate system state when the instruction at a particular address is reached.

- Parameters

-

[in] value is ignored by the processor. If required, a debugger can use it to store additional information about the breakpoint.

◆ __BKPT [4/4]

| #define __BKPT | ( | value | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_gcc.h>

Breakpoint.

Causes the processor to enter Debug state. Debug tools can use this to investigate system state when the instruction at a particular address is reached.

- Parameters

-

[in] value is ignored by the processor. If required, a debugger can use it to store additional information about the breakpoint.

◆ __CLZ

| #define __CLZ __clz |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armcc.h>

Count leading zeros.

Counts the number of leading zeros of a data value.

- Parameters

-

[in] value Value to count the leading zeros

- Returns

- number of leading zeros in value

◆ __CMSIS_GCC_OUT_REG [1/3]

| #define __CMSIS_GCC_OUT_REG | ( | r | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang.h>

◆ __CMSIS_GCC_OUT_REG [2/3]

| #define __CMSIS_GCC_OUT_REG | ( | r | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang_ltm.h>

◆ __CMSIS_GCC_OUT_REG [3/3]

| #define __CMSIS_GCC_OUT_REG | ( | r | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_gcc.h>

◆ __CMSIS_GCC_RW_REG [1/2]

| #define __CMSIS_GCC_RW_REG | ( | r | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang.h>

◆ __CMSIS_GCC_RW_REG [2/2]

| #define __CMSIS_GCC_RW_REG | ( | r | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_gcc.h>

◆ __CMSIS_GCC_USE_REG [1/3]

| #define __CMSIS_GCC_USE_REG | ( | r | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang.h>

◆ __CMSIS_GCC_USE_REG [2/3]

| #define __CMSIS_GCC_USE_REG | ( | r | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang_ltm.h>

◆ __CMSIS_GCC_USE_REG [3/3]

| #define __CMSIS_GCC_USE_REG | ( | r | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_gcc.h>

◆ __DMB [1/3]

| #define __DMB | ( | void | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armcc.h>

Data Memory Barrier.

Ensures the apparent order of the explicit memory operations before and after the instruction, without ensuring their completion.

◆ __DMB [2/3]

| #define __DMB | ( | void | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang.h>

Data Memory Barrier.

Ensures the apparent order of the explicit memory operations before and after the instruction, without ensuring their completion.

◆ __DMB [3/3]

| #define __DMB | ( | void | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang_ltm.h>

Data Memory Barrier.

Ensures the apparent order of the explicit memory operations before and after the instruction, without ensuring their completion.

◆ __DSB [1/3]

| #define __DSB | ( | void | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armcc.h>

Data Synchronization Barrier.

Acts as a special kind of Data Memory Barrier. It completes when all explicit memory accesses before this instruction complete.

◆ __DSB [2/3]

| #define __DSB | ( | void | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang.h>

Data Synchronization Barrier.

Acts as a special kind of Data Memory Barrier. It completes when all explicit memory accesses before this instruction complete.

◆ __DSB [3/3]

| #define __DSB | ( | void | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang_ltm.h>

Data Synchronization Barrier.

Acts as a special kind of Data Memory Barrier. It completes when all explicit memory accesses before this instruction complete.

◆ __ISB [1/3]

| #define __ISB | ( | void | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armcc.h>

Instruction Synchronization Barrier.

Instruction Synchronization Barrier flushes the pipeline in the processor, so that all instructions following the ISB are fetched from cache or memory, after the instruction has been completed.

◆ __ISB [2/3]

| #define __ISB | ( | void | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang.h>

Instruction Synchronization Barrier.

Instruction Synchronization Barrier flushes the pipeline in the processor, so that all instructions following the ISB are fetched from cache or memory, after the instruction has been completed.

◆ __ISB [3/3]

| #define __ISB | ( | void | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang_ltm.h>

Instruction Synchronization Barrier.

Instruction Synchronization Barrier flushes the pipeline in the processor, so that all instructions following the ISB are fetched from cache or memory, after the instruction has been completed.

◆ __NOP [1/4]

| #define __NOP __nop |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armcc.h>

No Operation.

No Operation does nothing. This instruction can be used for code alignment purposes.

◆ __NOP [2/4]

| #define __NOP __builtin_arm_nop |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang.h>

No Operation.

No Operation does nothing. This instruction can be used for code alignment purposes.

◆ __NOP [3/4]

| #define __NOP __builtin_arm_nop |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang_ltm.h>

No Operation.

No Operation does nothing. This instruction can be used for code alignment purposes.

◆ __NOP [4/4]

| #define __NOP | ( | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_gcc.h>

No Operation.

No Operation does nothing. This instruction can be used for code alignment purposes.

◆ __RBIT [1/2]

| #define __RBIT __builtin_arm_rbit |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang.h>

Reverse bit order of value.

Reverses the bit order of the given value.

- Parameters

-

[in] value Value to reverse

- Returns

- Reversed value

◆ __RBIT [2/2]

| #define __RBIT __builtin_arm_rbit |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang_ltm.h>

Reverse bit order of value.

Reverses the bit order of the given value.

- Parameters

-

[in] value Value to reverse

- Returns

- Reversed value

◆ __REV [1/3]

| #define __REV __rev |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armcc.h>

Reverse byte order (32 bit)

Reverses the byte order in unsigned integer value. For example, 0x12345678 becomes 0x78563412.

- Parameters

-

[in] value Value to reverse

- Returns

- Reversed value

◆ __REV [2/3]

| #define __REV | ( | value | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang.h>

Reverse byte order (32 bit)

Reverses the byte order in unsigned integer value. For example, 0x12345678 becomes 0x78563412.

- Parameters

-

[in] value Value to reverse

- Returns

- Reversed value

◆ __REV [3/3]

| #define __REV | ( | value | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang_ltm.h>

Reverse byte order (32 bit)

Reverses the byte order in unsigned integer value. For example, 0x12345678 becomes 0x78563412.

- Parameters

-

[in] value Value to reverse

- Returns

- Reversed value

◆ __REV16 [1/2]

| #define __REV16 | ( | value | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang.h>

Reverse byte order (16 bit)

Reverses the byte order within each halfword of a word. For example, 0x12345678 becomes 0x34127856.

- Parameters

-

[in] value Value to reverse

- Returns

- Reversed value

◆ __REV16 [2/2]

| #define __REV16 | ( | value | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang_ltm.h>

Reverse byte order (16 bit)

Reverses the byte order within each halfword of a word. For example, 0x12345678 becomes 0x34127856.

- Parameters

-

[in] value Value to reverse

- Returns

- Reversed value

◆ __REVSH [1/2]

| #define __REVSH | ( | value | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang.h>

Reverse byte order (16 bit)

Reverses the byte order in a 16-bit value and returns the signed 16-bit result. For example, 0x0080 becomes 0x8000.

- Parameters

-

[in] value Value to reverse

- Returns

- Reversed value

◆ __REVSH [2/2]

| #define __REVSH | ( | value | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang_ltm.h>

Reverse byte order (16 bit)

Reverses the byte order in a 16-bit value and returns the signed 16-bit result. For example, 0x0080 becomes 0x8000.

- Parameters

-

[in] value Value to reverse

- Returns

- Reversed value

◆ __ROR

| #define __ROR __ror |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armcc.h>

Rotate Right in unsigned value (32 bit)

Rotate Right (immediate) provides the value of the contents of a register rotated by a variable number of bits.

- Parameters

-

[in] op1 Value to rotate [in] op2 Number of Bits to rotate

- Returns

- Rotated value

◆ __SEV [1/4]

| #define __SEV __sev |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armcc.h>

Send Event.

Send Event is a hint instruction. It causes an event to be signaled to the CPU.

◆ __SEV [2/4]

| #define __SEV __builtin_arm_sev |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang.h>

Send Event.

Send Event is a hint instruction. It causes an event to be signaled to the CPU.

◆ __SEV [3/4]

| #define __SEV __builtin_arm_sev |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang_ltm.h>

Send Event.

Send Event is a hint instruction. It causes an event to be signaled to the CPU.

◆ __SEV [4/4]

| #define __SEV | ( | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_gcc.h>

Send Event.

Send Event is a hint instruction. It causes an event to be signaled to the CPU.

◆ __WFE [1/4]

| #define __WFE __wfe |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armcc.h>

Wait For Event.

Wait For Event is a hint instruction that permits the processor to enter a low-power state until one of a number of events occurs.

◆ __WFE [2/4]

| #define __WFE __builtin_arm_wfe |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang.h>

Wait For Event.

Wait For Event is a hint instruction that permits the processor to enter a low-power state until one of a number of events occurs.

◆ __WFE [3/4]

| #define __WFE __builtin_arm_wfe |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang_ltm.h>

Wait For Event.

Wait For Event is a hint instruction that permits the processor to enter a low-power state until one of a number of events occurs.

◆ __WFE [4/4]

| #define __WFE | ( | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_gcc.h>

Wait For Event.

Wait For Event is a hint instruction that permits the processor to enter a low-power state until one of a number of events occurs.

◆ __WFI [1/4]

| #define __WFI __wfi |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armcc.h>

Wait For Interrupt.

Wait For Interrupt is a hint instruction that suspends execution until one of a number of events occurs.

◆ __WFI [2/4]

| #define __WFI __builtin_arm_wfi |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang.h>

Wait For Interrupt.

Wait For Interrupt is a hint instruction that suspends execution until one of a number of events occurs.

◆ __WFI [3/4]

| #define __WFI __builtin_arm_wfi |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang_ltm.h>

Wait For Interrupt.

Wait For Interrupt is a hint instruction that suspends execution until one of a number of events occurs.

◆ __WFI [4/4]

| #define __WFI | ( | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_gcc.h>

Wait For Interrupt.

Wait For Interrupt is a hint instruction that suspends execution until one of a number of events occurs.

Function Documentation

◆ __attribute__() [1/3]

| __attribute__ | ( | (always_inline) | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armcc.h>

Reverse bit order of value.

Unsigned Saturate.

Signed Saturate.

Reverses the bit order of the given value.

- Parameters

-

[in] value Value to reverse

- Returns

- Reversed value

Saturates a signed value.

- Parameters

-

[in] value Value to be saturated [in] sat Bit position to saturate to (1..32)

- Returns

- Saturated value

Saturates an unsigned value.

- Parameters

-

[in] value Value to be saturated [in] sat Bit position to saturate to (0..31)

- Returns

- Saturated value

◆ __attribute__() [2/3]

| __attribute__ | ( | (section(".rev16_text")) | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armcc.h>

Reverse byte order (16 bit)

Reverses the byte order within each halfword of a word. For example, 0x12345678 becomes 0x34127856.

- Parameters

-

[in] value Value to reverse

- Returns

- Reversed value

◆ __attribute__() [3/3]

| __attribute__ | ( | (section(".revsh_text")) | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armcc.h>

Reverse byte order (16 bit)

Reverses the byte order in a 16-bit value and returns the signed 16-bit result. For example, 0x0080 becomes 0x8000.

- Parameters

-

[in] value Value to reverse

- Returns

- Reversed value

◆ __CLZ()

| __STATIC_FORCEINLINE uint8_t __CLZ | ( | uint32_t | value | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang.h>

Count leading zeros.

Counts the number of leading zeros of a data value.

- Parameters

-

[in] value Value to count the leading zeros

- Returns

- number of leading zeros in value

◆ __DMB()

| __STATIC_FORCEINLINE void __DMB | ( | void | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_gcc.h>

Data Memory Barrier.

Ensures the apparent order of the explicit memory operations before and after the instruction, without ensuring their completion.

◆ __DSB()

| __STATIC_FORCEINLINE void __DSB | ( | void | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_gcc.h>

Data Synchronization Barrier.

Acts as a special kind of Data Memory Barrier. It completes when all explicit memory accesses before this instruction complete.

◆ __ISB()

| __STATIC_FORCEINLINE void __ISB | ( | void | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_gcc.h>

Instruction Synchronization Barrier.

Instruction Synchronization Barrier flushes the pipeline in the processor, so that all instructions following the ISB are fetched from cache or memory, after the instruction has been completed.

◆ __RBIT()

| __STATIC_FORCEINLINE uint32_t __RBIT | ( | uint32_t | value | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_gcc.h>

Reverse bit order of value.

Reverses the bit order of the given value.

- Parameters

-

[in] value Value to reverse

- Returns

- Reversed value

◆ __REV()

| __STATIC_FORCEINLINE uint32_t __REV | ( | uint32_t | value | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_gcc.h>

Reverse byte order (32 bit)

Reverses the byte order in unsigned integer value. For example, 0x12345678 becomes 0x78563412.

- Parameters

-

[in] value Value to reverse

- Returns

- Reversed value

◆ __REV16()

| __STATIC_FORCEINLINE uint32_t __REV16 | ( | uint32_t | value | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_gcc.h>

Reverse byte order (16 bit)

Reverses the byte order within each halfword of a word. For example, 0x12345678 becomes 0x34127856.

- Parameters

-

[in] value Value to reverse

- Returns

- Reversed value

◆ __REVSH()

| __STATIC_FORCEINLINE int16_t __REVSH | ( | int16_t | value | ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_gcc.h>

Reverse byte order (16 bit)

Reverses the byte order in a 16-bit value and returns the signed 16-bit result. For example, 0x0080 becomes 0x8000.

- Parameters

-

[in] value Value to reverse

- Returns

- Reversed value

◆ __ROR()

| __STATIC_FORCEINLINE uint32_t __ROR | ( | uint32_t | op1, |

| uint32_t | op2 ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang.h>

Rotate Right in unsigned value (32 bit)

Rotate Right (immediate) provides the value of the contents of a register rotated by a variable number of bits.

- Parameters

-

[in] op1 Value to rotate [in] op2 Number of Bits to rotate

- Returns

- Rotated value

◆ __SSAT()

| __STATIC_FORCEINLINE int32_t __SSAT | ( | int32_t | val, |

| uint32_t | sat ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang.h>

Signed Saturate.

Saturates a signed value.

- Parameters

-

[in] value Value to be saturated [in] sat Bit position to saturate to (1..32)

- Returns

- Saturated value

◆ __USAT()

| __STATIC_FORCEINLINE uint32_t __USAT | ( | int32_t | val, |

| uint32_t | sat ) |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armclang.h>

Unsigned Saturate.

Saturates an unsigned value.

- Parameters

-

[in] value Value to be saturated [in] sat Bit position to saturate to (0..31)

- Returns

- Saturated value

Variable Documentation

◆ sat

| uint32_t sat |

#include <port/ucontroller/nxp/lpc17xx/bootloader/inc/cmsis_armcc.h>